Atmel公司工程师的文章,原名AVR186:Best Practices for the PCB layout of Oscillators

我最近研究晶振布线,看到本文后顺手翻译过来,供大家参考。原文Google随手可得。

电容太小,中间难以过导线,无法按照图中去布线,但是参考本文仍然有助于加深理解。

本文的PDF版下载http://wenku.baidu.com/view/58ec7d32f111f18583d05a5f.html?st=1

1. 简介

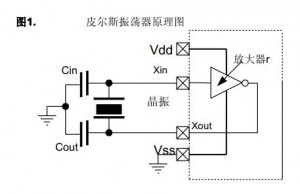

我们通常所使用的振荡器是皮尔斯振荡器(Pierce oscillator),它是由放大器和一个带宽很窄的选频滤波器组成.放大器集成在芯片内部,滤波器则是由晶振 (crystal)或陶瓷谐振腔(ceramic resonator)构成,如图1:

该系统的输入阻抗在谐振频率上很低,而在其它频率上则很高.其高阻抗的特性使它更容易受到周围电路的干 扰.此外, 为了降低功耗,目前振荡器的电平一般限制在 1V以下, 这进一步降低了其抗干 扰的能力.

2. 描述

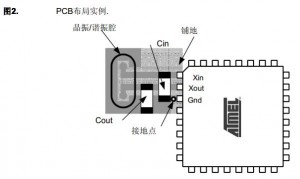

为了增强振荡器抗干 扰的能力,PCB布局十分重要.如图2:

3. 设计指南

为降低由振荡器引发问题的风险,我们建议您遵循如下设计指南:

• 晶振或谐振腔对于寄生电容和其它信号带来的干 扰十分敏感. 因此布局时要远离高速信号线,以降低 Xin与Xout管脚和其它信号线之间的容性耦合.

• 晶振的线路与数字信号线越远越好, 尤其是时钟信号线或频繁改变状态的信号线. 信号之间的串扰会影响振荡器的波形.

• 负载电容的接地点需要足够的短,以避免来自USB, RS232, LIN, PWM与电源线的返回电流.

• 负载电容的漏电流要小,热稳定性要好 (如NPO或COG型号).

• 两个负载电容需要挨的很近。

• 负载电容中的Cin优先靠近GND和Xin管脚.

• 寄生电容会降低增益裕度. 因此要尽可能的降低寄生电容,下面给出寄生电容的典型值:

– Xin对地 : 1pF

– Xout对地 : 2pF

– Xin对Xlout : 0.5pF

这些数值与元件的封装也有少许关联.

• 为降低 Xin与Xout两管脚之间的寄生电容,就要使其引出的两条线离得越远越好.

• 在晶振下方需要铺地,并与振荡器的地相连.

•将晶振和陶瓷谐振腔所需要的外部电容与晶振外壳一同接地(该条附原文:Connect the external capacitors needed for the crystal and the ceramic resonator operation as well as the crystal housing to the ground plane).

• 如果是单层板, 建议在振荡器电路各元件周围设置一保护环(guard ring),并将其连接到相应的接地引脚.